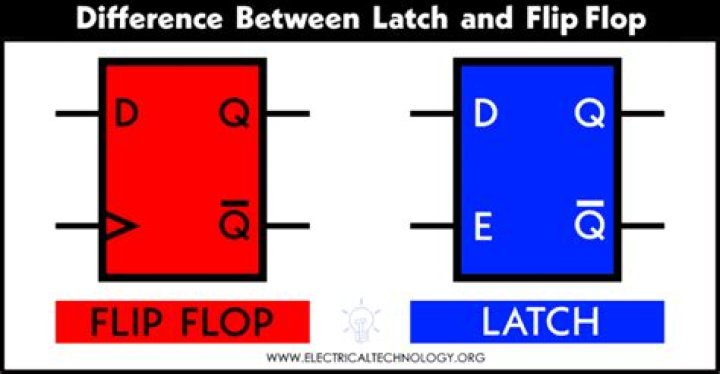

Why do we use flip flops instead of latches

William Burgess

William Burgess Generally designers prefer flip flops over latches because of this edge-triggered property, which makes the behavior of the timing simple and eases design interpretation. Latch-based designs have small die size and are more successful in high-speed designs where clock frequency is in GHz.

Why is Flip Flop better than latch?

You can design it using Logic gates. Flip-flop is sensitive to the applied input and the clock signal. Latches are sensitive to the applied input signal- only when enabled. It has a slow operating speed.

Why we are using flip flops?

A flip flop is an electronic circuit with two stable states that can be used to store binary data. The stored data can be changed by applying varying inputs. Flip-flops and latches are fundamental building blocks of digital electronics systems used in computers, communications, and many other types of systems.

Why are latches not preferred?

* Flip Flops are preferred in RTL design because the use of latches will infer potential Race condition within the design which ultimately leads to erroneous results. * Latches are prone to glitches which are unwanted in the design and that is why Flip flops are preferred.What is the main difference between latch and flip flop?

Flip-flop is a bistable device i.e., it has two stable states that are represented as 0 and 1. Latch is also a bistable device whose states are also represented as 0 and 1. It checks the inputs but changes the output only at times defined by the clock signal or any other control signal.

Which problem of latch-based designs can be solved using flip flops?

Latch-based designs are preferred in case of clock frequency in GHz (in high-speed designs). In flip-flop-based high-speed designs, maintaining clock skew is a problem, but latches ease this problem.

Which consumes more power latch or flip-flop?

More power is consumed by the Flip-Flop. … The latch is sensitive to the input and as long as it is ‘On’, we can transmit the data. Flip-Flop is sensitive to the clock signals and until there is a change in the input clock signal, it never changes the output.

Why is inferring latches a bad design practice and how can you accidentally infer a latch?

All inferred latches become inferred flip-flops. This is usually a bad idea because it can unnecessarily increases the gate count, create more routing, and impact timing.What causes latches to be created by Synthesis Software?

Latches are created when you create a combinational process or conditional assignment (in VHDL) or a combinational always block (in Verilog) with an output that is not assigned under all possible input conditions. This creates what is known as incomplete assignment by the synthesis tools.

Which flip flop is used as a latch?RS flip-flop is used as a latch.

Article first time published onWhy JK flip flop is widely used?

JK Flip Flop is a universal flip-flop that makes the circuit toggle between two states and is widely used in shift registers, counters, PWM and computer applications. … Flip Flop comes with two stable states and is mainly used to store the state information of any circuit.

Which flip flop is widely used and why?

Originally Answered: Why d flip flop is widely used? It is less complex than other flipflops (only one input and one output). It can provide a finite amount of delay by using a favourable clock pulse. It is transparent because it transfers the input to the output.

Where are latches and flip flops used?

It is the basic storage element in sequential logic. Flip-flops and latches are fundamental building blocks of digital electronics systems used in computers, communications, and many other types of systems. Flip-flops and latches are used as data storage elements.

What is one disadvantage of an SR flip-flop?

When the S and R inputs of an SR flipflop are at logical 1, then the output becomes unstable and it is known as a race condition. So, the main disadvantage of the SR flip flop is invalid output when both inputs are high.

What is the main difference between ad latch with enable and ad flip-flop?

The difference between a D-type latch and a D-type flip-flop is that a latch does not have a clock signal to change state whereas a flip-flop always does. The D flip-flop is an edge triggered device which transfers input data to Q on clock rising or falling edge.

What is the difference between latch based design and flip flop based design?

The difference between a latch and a flip-flop is that a latch is level-triggered (outputs can change as soon as the inputs changes) and Flip-Flop is edge-triggered (only changes state when a control signal goes from high to low or low to high).

What is the difference between D flip flop and T flip flop?

D flip flop has an inverter in the R input place. Where as, T flip flop does not have an inverter. D flip flop is no different than a delay element which is used to store data where as T flip flop complements the data in a continuous manner which is also called “toggling”.

Why is latch asynchronous?

Latches are asynchronous, which means that the output changes very soon after the input changes. Most computers today, on the other hand, are synchronous, which means that the outputs of all the sequential circuits change simultaneously to the rhythm of a global clock signal.

Why are latches not preferred in synthesized design?

Latches can lead to timing issues and race conditions. They may lead to combinatorial feedback – routing of the output back to the input – which can be unpredictable. To avoid creating inferred latches: Include all the branches of an if or case statement.

What causes latches in VHDL?

Latches are inferred in VHDL by using the IF statement without its matching ELSE. This causes the synthesis to make the logical decision to “hold” the value of a signal when not told to do anything else with it.

Why is latch bad?

As well as being frustrating and distressing for your baby, a poor breastfeeding latch can give you sore nipples. It may also mean your baby can’t drain your breast effectively, leading to poor weight gain, reducing your milk supply, and putting you at increased risk of blocked milk ducts and mastitis.

What is meant by inferring latches and how do you avoid it?

If you intended to infer a latch for the specified signal or variable, no action is required. Otherwise, to avoid a latch, explicitly assign a new value to the signal or variable in every possible path through the process statement.

What is meant by inferring latches how do you avoid it with an example?

A latch is inferred within a combinatorial block where the net is not assigned to a known value. Assign a net to itself will still infer a latch. Latches can also be inferred by missing signals form a sensitivity list and feedback loops.

Why latches are called a memory devices?

Why latches are called memory devices? Explanation: Latches can be memory devices, and can store one bit of data for as long as the device is powered. Once device is turned off, the memory gets refreshed. … Explanation: A latch has two stable states, following the principle of Bistable Multivibrator.

Why do the D flip flops received its designation or nomenclature as data flip flops?

14. Why do the D flip-flops receive its designation or nomenclature as ‘Data Flip-flops’? Explanation: Due to its capability to transfer the data into flip-flop. D-flip-flops stores the value on the data line.

Why is it called D flip flop?

A D-type flip-flop operates with a delay in input by one clock cycle. Thus, by cascading many D-type flip-flops delay circuits can be created, which are used in many applications such as in digital television systems. A D-type flip-flop is also known as a D flip-flop or delay flip-flop.

Which flip flop is used in shift register?

A simple Shift Register can be made using only D-type flip-Flops, one flip-Flop for each data bit. The output from each flip-Flop is connected to the D input of the flip-flop at its right. Shift registers hold the data in their memory which is moved or “shifted” to their required positions on each clock pulse.

What is a flip flop explain the RS and JK flip flop?

It has two states as logic 1(High) and logic 0(low) states. A flip flop is a sequential circuit which consists of a single binary state of information or data. The digital circuit is a flip flop which has two outputs and are of opposite states. It is also known as a Bistable Multivibrator.

Which flip flop is commonly used?

The flip flop stores only binary data that has two states they are logic 1 and logic 0. The set-reset, JK, delay, and trigger or toggle are the most commonly used flip flops.

Which flip flop is widely used?

The most common types of flip flops are: SR flip-flop: Is similar to an SR latch. Besides the CLOCK input, an SR flip-flop has two inputs, labeled SET and RESET. If the SET input is HIGH when the clock is triggered, the Q output goes HIGH.

What is the difference between a latch and a flip flop design and define all flip flops with their state tables?

Latches & FFs are the simple kinds of sequential circuits, and also building blocks for difficult sequential circuits. … The major difference between latches and flip-flops is that a latch doesn’t contain any clock signal whereas flip-flops consist of a clock signal.